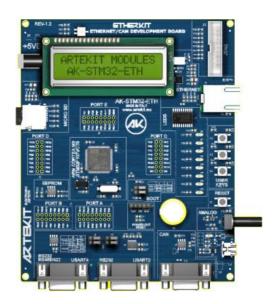

# AK-STM32-ETH Development Board

Reference manual

# **Contents**

| About this document                 | 3                            |

|-------------------------------------|------------------------------|

| Revision history                    | 3                            |

| Contact information                 | 3                            |

| Life support policy                 | 3                            |

| Copyright information               | 3                            |

| Specifications                      | 4                            |

| General description                 | 4                            |

| Main components                     | 4                            |

| Block diagram                       | Error! Bookmark not defined. |

| Environmental requirements          | 4                            |

| Handling the board                  | 4                            |

| Board overview                      | 4                            |

| Components description              | 5                            |

| MPU                                 | 5                            |

| Clocks                              | 5                            |

| Battery                             | 6                            |

| Power                               | 6                            |

| GPS                                 | Error! Bookmark not defined. |

| Micro SD socket                     | 6                            |

| JTAG connector                      | 6                            |

| RS232 connector                     | 6                            |

| EEPROM                              | 6                            |

| Display                             | 7                            |

| MCU connections                     |                              |

| Hardware description                | g                            |

| 1 - External power supply connector | Error! Bookmark not defined. |

|                                     | g                            |

| 3.8.4 - Jumper settings             | 10                           |

# About this document

# **Revision history**

The table below displays the revision history for the chapters in this manual.

| Chapter | Date          | Revision | Changes made      |

|---------|---------------|----------|-------------------|

| All     | November 2011 | 1.0      | First publication |

## **Contact information**

For the latest news, upgrades and information about Artekit products, visit the Artekit web site at <a href="http://www.artekit.eu/support">http://www.artekit.eu/support</a>

For additional information about Artekit products, consult the sources below.

| Information type  | Resource           |

|-------------------|--------------------|

| Technical support | support@artekit.eu |

| Literature        | www.artekit.eu     |

| Sales             | sales@artekit.eu   |

| Products forum    | www.artekit.eu     |

# Life support policy

Artekit Italy products are not indented or authorized for use as critical components in life support devices or systems without the express written approval from Artekit Italy. Those devices may include devices for supporting or sustaining life, devices for surgical implant into the body or any other device whose failure to perform correctly could result in life support failure.

# **Copyright information**

This document is copyright © 2012 Artekit Italy. All rights reserved. Any person may view, copy, print and distribute this document or any portion of this document for informational purposes only as long as the copyright notice remains included.

# **Specifications**

# **General description**

The AK-STM32-ETH development board is a full-featured hardware platform to evaluate the STMicroelectronics STM32F107 Connectivity Line ARM Cortex M3 MPU. This board support 10/100 Ethernet adapter, CAN 2.0, RS-232/485, USB OTG, 2x16 LCD display, 8KB EEPROM and MicroSD socket. The complete schematics of the boards are provided allowing the users to experiment with the MPU peripherals, to add external devices and enabling designers to begin the development or testing custom systems.

# Main components

The AK-STM32-ETH Development board features the following components:

- ST Microelectronics STM32F107VCT6 ARM Cortex M3 in TQFP100 packaging.

- 10/100 Mb Ethernet adapter with link/speed LED's.

- M24C64 8KB EEPROM.

- 1 RS232 (TX/RX only).

- 1 RS232/RS485.

- USB OTG 2.0 FULL SPEED.

- CAN 2.0

- 2 lines x16 characters LCD display (5x7 matrix).

- Backup RTC battery.

- Micro SD socket.

- Precision voltage reference for AD.

- Potentiometer for AD testing.

- 8 User LED's.

- 3 User KEY's.

- Standard 20-pin ARM JTAG connector .

- Powered from USB cable or external 5V DC power supply.

# **Environmental requirements**

The AK-STM32-ETH development board must be stored between –40° C and 100° C. The recommended operating temperature is between 0° and 55° C.

The AK-STM32-ETH development board can be damaged without proper anti-static handling.

# Handling the board

When handling the board, it is important to observe the following precaution:

Static discharge precaution — Without proper anti-static handling the board can be damaged. Therefore, take anti-static precautions while handling the board.

# **Components description**

The following section describes in detail the main components of the development board.

#### **MPU**

ST Microelectronics STM32F107VCT6 ARM Cortex M3 MPU

- Core: ARM 32-bit Cortex™-M3 CPU 72 MHz maximum frequency, 1.25 DMIPS/MHz (Dhrystone 2.1) performance at 0 wait state memory access Single-cycle multiplication and hardware division

- Memories: 256 Kbytes of Flash memory 64 Kbytes of SRAM 20KB static RAM,

- Clock, reset and supply management 2.0 to 3.6 V application supply and I/Os POR, PDR, and programmable voltage detector (PVD)

- 4-to-16 MHz crystal oscillator Internal 8 MHz factory-trimmed RC Internal 40 kHz RC PLL for CPU clock –

32 kHz oscillator for RTC with calibration

- Low power Sleep, Stop and Standby modes VBAT supply for RTC and backup registers

- 2 x 12-bit, 1 μs A/D converters (up to 16 channels) Conversion range: 0 to 3.6 V Dual-sample and hold capability – Temperature sensor

- 2 × 12-bit D/A converters

- DMA 12-channel DMA controller Peripherals supported: timers, ADCs, DAC, I2Ss, SPIs, I2Cs and USARTs

- Up to 80 I/Os, all mappable on 16 external interrupt vectors, and almost all 5 V-tolerant except for analog inputs

- Debug mode Serial wire debug (SWD) & JTAG interfaces

- Timers: 10 timers Four 16-bit timers, each with up to 4 IC/OC/PWM or pulse counter

- 1 × 16-bit motor control PWM timer with dead-time generation and emergency stop

- 2 × watchdog timers (Independent and Window)

- SysTick timer: a 24-bit downcounter

- 2 × 16-bit basic timers to drive the DAC

- Up to 14 communication interfaces with pinout remap capability

- Up to 2 x I2C interfaces (SMBus/PMBus) Up to 3 USARTs (ISO 7816 interface, LIN, IrDA capability, modem control)

- Up to 2 × I2C interfaces (SMBus/PMBus)

- Up to 5 USARTs (ISO 7816 interface, LIN,

- USB 2.0 full-speed interface IrDA capability, modem control)

- Up to 3 SPIs (18 Mbit/s), 2 with a multiplexed I2S interface that offers audio class accuracy via advanced PLL schemes

- 2 × CAN interfaces (2.0B Active) with 512 bytes of dedicated SRAM

- USB 2.0 full-speed device/host/OTG controller with on-chip PHY that supports HNP/SRP/ID with 1.25 Kbytes of dedicated SRAM

- 10/100 Ethernet MAC with dedicated DMA and SRAM (4 Kbytes): IEEE1588 hardware support, MII/RMII available on all packages

#### Clocks

- Main clock at 25MHz, on board quartz.

- RTC Clock at 32768 Hz, on board quartz.

#### **Battery**

3V Non rechargeable LiMg battery for MCU RTC retention.

#### **Power**

1 power regulators.

LD1117-3.3 LDO Regulator - 3.3V 800mA board power supply

**NOTE**: The board can be fully powered through the standard USB cable.

#### Micro SD socket

Standard micro SD socket.

Access mode: SPICard detect: YesWrite protect: No

#### **JTAG** connector

Standard 20-pin ARM JTAG connector

- 2 rows 10 pin 2.54mm

- Support any ARM JTAG cable

**NOTE**: The board was tested with the following JTAG adapters:

- Artekit AK-LINK

- OpenJTAG Project (http://www.openjtag.org)

- Egnite Turtelizer2 (http://www.ethernut.de)

- Keil ULINK2

- Keil ULINK-ME

- Segger J-Link

#### **Ethernet connector**

10/100 Mb with LINK and SPEED LED's

#### **RS232** connectors

The RS232 connector enables the communication from the MPU with the external world. The jumpers J8 and J15 set the MCU communication using RS232 or RS485/422 modes. Please refer to jumper setting options.

#### **EEPROM**

The board has an 8KB EEPROM to store user data. The component is a STMicroelectronics M24C64-WMN6TP device, connected to the MCU through I2C interface. The device features are:

- 400 KHz Fast Mode

- 100 KHz Standard Mode

- 2.5 to 5V

- Write Control Input

- Byte and Page write

- Random and Sequential Read modes

- Self-timed programming cycle

- Automatic address incrementing

- Enhanced ESD/latch-up protection

- More than 1 Million write cycles

- More than 40-year data retention

#### **Display**

Gleichman Electronics Model GE-C1602B-NYG-ET/R.

- 16 characters x 2 Lines

- 7x5 matrix

- Powered at 5V

- 4 bit data bus

- Backlight: No

- Dimension: 80.0 x 36.0 x 13.5(MAX) mm.

- View area: 66.0 x 16.0 mm.

- Active area: 56.20 x 11.5 mm.

- Dot size: 0.55 x 0.65 mm.

- Dot pitch: 0.60 x 0.70 mm.

- Character size: 2.95 x 5.55 mm.

- Character pitch: 3.55 x 5.95 mm.

- LCD type: STN Negative, Blue Transmissive.

- Duty: 1/16

- View direction: 6 o'clock

#### **CAN Connector**

CAN 2.0B connector

### **MCU** connections

| PA11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PIN NAME     | PIN# | DESCRIPTION                                       | COMMENTS                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|---------------------------------------------------|---------------------------|

| PA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |      |                                                   |                           |

| PA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |      |                                                   | Active low                |

| PA3         26         USER I/O         Unprotected           PA4         29         USER I/O         Unprotected           PA5         30         SPI1, SCK. Connected to SD Memory           PA6         31         SPI1, MISO. Connected to SD Memory           PA7         32         SPI1, MOSI. Connected to SD Memory           PA8         67         USER I/O         Unprotected           PA9         68         +VBUS detect. Detect external USB power         Active high           PA10         69         USB ID signal         Active high - Unprotected           PA11         70         USB M. Connected to USB-B connector           PA13         72         JTAG TMS/SWDIO         Unprotected           PA14         76         JTAG TMS/SWDIO         Unprotected           PA14         76         JTAG TCK/SWCLK         Unprotected           PA15         77         JTAG TDI         Unprotected           PB1         35         RS485 DE control         Active high           PB1         36         RS485 DE control         Active low           PB2         37         Boot control. Could be used as I/O. See J2 switch         Unprotected           PB3         91         JTAG TDO         <                                                                                                                                                                                                                                            |              |      |                                                   |                           |

| PA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |      | <u> </u>                                          |                           |

| PA6   30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |      |                                                   | Unprotected               |

| PA6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |      |                                                   | Unprotected               |

| PA7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |      |                                                   |                           |

| PA8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |      |                                                   |                           |

| PA9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |      |                                                   |                           |

| PA10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |      |                                                   |                           |

| PA11         70         USB_M. Connected to USB-B connector           PA12         71         USB_P. Connected to USB-B connector           PA13         72         JTAG TMS/SWDIO         Unprotected           PA14         76         JTAG TCK/SWCLK         Upprotected           PA15         77         JTAG TDI         Unprotected           PB0         35         RS485 DE control         Active low           PB1         36         RS485 RE control         Active low           PB2         37         Boot control. Could be used as I/O. See J2 switch         Unprotected           PB3         89         JTAG TDO         Unprotected           PB4         90         JTAG TRST         Upprotected           PB5         91         USER I/O         Unprotected           PB6         92         USER I/O         Unprotected           PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SCL. Connected to EEPROM         PB9           PB9         96         I2C_SDA. Connected to EEPROM         Upprotected           PB11         48         Drive TXEN signal to the DP83848J Ethernet MAC         PB13           PB13         52         Dr                                                                                                                                                                                                                                                        |              |      |                                                   |                           |

| PA12         71         USB_P. Connected to USB-B connector           PA13         72         JTAG TMS/SWDIO         Unprotected           PA14         76         JTAG TCK/SWCLK         Unprotected           PA15         77         JTAG TDI         Unprotected           PB0         35         RS485 DE control         Active high           PB1         36         RS485 RE control         Active low           PB2         37         Boot control. Could be used as I/O. See J2 switch         Unprotected           PB3         89         JTAG TDO         Unprotected           PB4         90         JTAG TRST         Unprotected           PB5         91         USER I/O         Unprotected           PB6         92         USER I/O         Unprotected           PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SCL. Connected to EEPROM         Unprotected           PB9         96         I2C_SDA. Connected to EEPROM         Unprotected           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXD1 signal to the DP83848J Ethernet MAC         Drive TXD1 signal to the DP83848J Ethernet MAC                                                                                                                                                                                                                                                 |              |      | USB ID signal                                     | Active high - Unprotected |

| PA13         72         JTAG TMS/SWDIO         Unprotected           PA14         76         JTAG TCK/SWCLK         Unprotected           PA15         77         JTAG TDI         Unprotected           PB0         35         RS485 DE control         Active high           PB1         36         RS485 RE control         Active low           PB2         37         Boot control. Could be used as I/O. See J2 switch         Unprotected           PB3         89         JTAG TDO         Unprotected           PB4         90         JTAG TST         Unprotected           PB5         91         USER I/O         Unprotected           PB6         92         USER I/O         Unprotected           PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SCL. Connected to EEPROM         Unprotected           PB9         96         I2C_SDA. Connected to EEPROM         Unprotected           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXEN signal to the DP83848J Ethernet MAC         PB18           PB13         52         Drive TXD1 signal to the DP83848J Ethernet MAC         Unprotected                                                                                                                                                                                                                                                             | PA11         | 70   | USB_M. Connected to USB-B connector               |                           |

| PA14         76         JTAG TCK/SWCLK         Unprotected           PA15         77         JTAG TDI         Unprotected           PB0         35         RS485 DE control         Active low           PB1         36         RS485 RE control         Active low           PB2         37         Boot control. Could be used as I/O. See J2 switch         Unprotected           PB3         89         JTAG TDO         Unprotected           PB4         90         JTAG TRST         Unprotected           PB5         91         USER I/O         Unprotected           PB6         92         USER I/O         Unprotected           PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SCL. Connected to EEPROM         PB9           PB9         96         I2C_SDA. Connected to EEPROM         PB1           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXD0 signal to the DP83848J Ethernet MAC         PB18           PB13         52         Drive TXD1 signal for the DP83848J Ethernet MAC         PB18           PB14         53         USER I/O         Unprotected           PC0         1                                                                                                                                                                                                                                                                 | PA12         | 71   | USB_P. Connected to USB-B connector               |                           |

| PA15         77         JTAG TDI         Unprotected           PB0         35         RS485 DE control         Active high           PB1         36         RS485 RE control         Active low           PB2         37         Boot control. Could be used as I/O. See J2 switch         Unprotected           PB3         89         JTAG TDO         Unprotected           PB4         90         JTAG TRST         Unprotected           PB5         91         USER I/O         Unprotected           PB6         92         USER I/O         Unprotected           PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SCL. Connected to EEPROM         Unprotected           PB9         96         I2C_SDA. Connected to EEPROM         Unprotected           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXD0 signal to the DP83848J Ethernet MAC         Drive TXD1 signal for the DP83848J Ethernet MAC           PB13         52         Drive TXD1 signal to the DP83848J Ethernet MAC         Unprotected           PB15         54         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used                                                                                                                                                                                                                     | PA13         | 72   | JTAG TMS/SWDIO                                    | Unprotected               |

| PB0         35         RS485 DE control         Active high           PB1         36         RS485 RE control         Active low           PB2         37         Boot control. Could be used as I/O. See J2 switch         Unprotected           PB3         89         JTAG TDO         Unprotected           PB4         90         JTAG TRST         Unprotected           PB5         91         USER I/O         Unprotected           PB6         92         USER I/O         Unprotected           PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SCL. Connected to EEPROM         Unprotected           PB9         96         I2C_SDA. Connected to EEPROM         Unprotected           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXEN signal to the DP83848J Ethernet MAC         Unprotected           PB12         51         Drive TXD0 signal to the DP83848J Ethernet MAC         Unprotected           PB14         53         USER I/O         Unprotected           PB15         54         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog                                                                                                                                                                                                                              | PA14         | 76   | JTAG TCK/SWCLK                                    | Unprotected               |

| PB0         35         RS485 DE control         Active high           PB1         36         RS485 RE control         Active low           PB2         37         Boot control. Could be used as I/O. See J2 switch         Unprotected           PB3         89         JTAG TDO         Unprotected           PB4         90         JTAG TRST         Unprotected           PB5         91         USER I/O         Unprotected           PB6         92         USER I/O         Unprotected           PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SCL. Connected to EEPROM         Unprotected           PB9         96         I2C_SDA. Connected to EEPROM         Unprotected           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXEN signal to the DP83848J Ethernet MAC         Drive TXDO signal to the DP83848J Ethernet MAC           PB13         52         Drive TXDO signal to the DP83848J Ethernet MAC         Unprotected           PB15         54         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16                                                                                                                                                                                                                       | PA15         | 77   | JTAG TDI                                          | Unprotected               |

| PB2         37         Boot control. Could be used as I/O. See J2 switch         Unprotected           PB3         89         JTAG TDO         Unprotected           PB4         90         JTAG TRST         Unprotected           PB5         91         USER I/O         Unprotected           PB6         92         USER I/O         Unprotected           PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SCL. Connected to EEPROM         PB1           PB9         96         I2C_SDA. Connected to EEPROM         Unprotected           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXEN signal to the DP83848J Ethernet MAC         Unprotected           PB13         52         Drive TXD1 signal to the DP83848J Ethernet MAC         Unprotected           PB14         53         USER I/O         Unprotected           PB15         54         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC         Unprotected           PC2         17         USER I/O                                                                                                                                                                                                                          | PB0          | 35   | RS485 DE control                                  |                           |

| PB3         89         JTAG TDO         Unprotected           PB4         90         JTAG TRST         Unprotected           PB5         91         USER I/O         Unprotected           PB6         92         USER I/O         Unprotected           PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SDA. Connected to EEPROM         Description           PB9         96         I2C_SDA. Connected to EEPROM         Unprotected           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXEN signal to the DP83848J Ethernet MAC         Description           PB12         51         Drive TXD1 signal to the DP83848J Ethernet MAC         Unprotected           PB13         52         Drive TXD1 signal to the DP83848J Ethernet MAC         Unprotected           PB14         53         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC         Unprotected           PC2         17         USER I/O         Unprotected           PC3         18         USER I/O                                                                                                                                                                                                                     | PB1          | 36   | RS485 RE control                                  | <u> </u>                  |

| PB3         89         JTAG TDO         Unprotected           PB4         90         JTAG TRST         Unprotected           PB5         91         USER I/O         Unprotected           PB6         92         USER I/O         Unprotected           PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SDA. Connected to EEPROM         PB9           PB9         96         I2C_SDA. Connected to EEPROM         Unprotected           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXEN signal to the DP83848J Ethernet MAC         PB12         51         Drive TXD1 signal to the DP83848J Ethernet MAC         PPB14         53         USER I/O         Unprotected           PB14         53         USER I/O         Unprotected         Unprotected           PB15         54         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC         Unprotected           PC2         17         USER I/O         Unprotected           PC3         18         USER                                                                                                                                                                                                                               | PB2          | 37   | Boot control. Could be used as I/O. See J2 switch | Unprotected               |

| PB4         90         JTAG TRST         Unprotected           PB5         91         USER I/O         Unprotected           PB6         92         USER I/O         Unprotected           PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SCL. Connected to EEPROM         Image: SCL. Sch. Connected to EEPROM           PB9         96         I2C_SDA. Connected to EEPROM         Unprotected           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXD0 signal to the DP83848J Ethernet MAC         PB12         51         Drive TXD1 signal to the DP83848J Ethernet MAC         PB13         52         Drive TXD1 signal to the DP83848J Ethernet MAC         Unprotected         PB14         53         USER I/O         Unprotected         PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V         PC1         16         Drive MDC signal to the DP83848J Ethernet MAC         Unprotected         PC2         17         USER I/O         Unprotected         Unprotected           PC2         17         USER I/O         Unprotected         Unprotected         Unprotected         PC6         34         USER I/O         Unprotected         PC6         63                                                                                                                                           | PB3          | 89   |                                                   |                           |

| PB5         91         USER I/O         Unprotected           PB6         92         USER I/O         Unprotected           PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SCL. Connected to EEPROM         I2C_SDA. Connected to EEPROM           PB9         96         I2C_SDA. Connected to EEPROM         Unprotected           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXD0 signal to the DP83848J Ethernet MAC         Inprotected           PB12         51         Drive TXD1 signal to the DP83848J Ethernet MAC         Unprotected           PB13         52         Drive TXD1 signal to the DP83848J Ethernet MAC         Unprotected           PB14         53         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC         Unprotected           PC2         17         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC4         33         USER I/O         Unprotected           PC5         34                                                                                                                                                                                                                      |              |      |                                                   |                           |

| PB6         92         USER I/O         Unprotected           PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SCL. Connected to EEPROM         I2C_SDA. Connected to EEPROM           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXEN signal to the DP83848J Ethernet MAC         PB12           PB13         51         Drive TXD0 signal to the DP83848J Ethernet MAC         PB13           PB14         53         USER I/O         Unprotected           PB15         54         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC         Unprotected           PC2         17         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC4         33         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected                                                                                                                                                                                                                                                         |              |      |                                                   | <u> </u>                  |

| PB7         93         User key 2 (K2)         Active low           PB8         95         I2C_SCL. Connected to EEPROM           PB9         96         I2C_SDA. Connected to EEPROM           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXEN signal to the DP83848J Ethernet MAC         PB12         51         Drive TXD0 signal to the DP83848J Ethernet MAC         Unprotected           PB13         52         Drive TXD1 signal to the DP83848J Ethernet MAC         Unprotected           PB14         53         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC         Unprotected           PC2         17         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC4         33         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC8         65                                                                                                                                                                                                                                       |              |      |                                                   | <u> </u>                  |

| PB8         95         I2C_SCL. Connected to EEPROM           PB9         96         I2C_SDA. Connected to EEPROM           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXEN signal to the DP83848J Ethernet MAC         PB12         51         Drive TXD0 signal to the DP83848J Ethernet MAC         PB13         52         Drive TXD1 signal to the DP83848J Ethernet MAC         Unprotected           PB14         53         USER I/O         Unprotected         Unprotected           PB15         54         USER I/O         Unprotected         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC         Unprotected           PC2         17         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC9         66                                                                                                                                                                                                                          |              |      |                                                   |                           |

| PB9         96         I2C_SDA. Connected to EEPROM           PB10         47         USER I/O         Unprotected           PB11         48         Drive TXEN signal to the DP83848J Ethernet MAC         Unprotected           PB12         51         Drive TXD0 signal to the DP83848J Ethernet MAC           PB13         52         Drive TXD1 signal to the DP83848J Ethernet MAC           PB14         53         USER I/O         Unprotected           PB15         54         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC           PC2         17         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC4         33         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC9         66         ENABLE signal from USB Power Protection Device STMPS2141         Active low           PC10         78                                                                                                                                                                                                                                  |              |      |                                                   |                           |

| PB10         47         USER I/O         Unprotected           PB11         48         Drive TXEN signal to the DP83848J Ethernet MAC           PB12         51         Drive TXD0 signal to the DP83848J Ethernet MAC           PB13         52         Drive TXD1 signal to the DP83848J Ethernet MAC           PB14         53         USER I/O         Unprotected           PB15         54         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC           PC2         17         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC4         33         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC8         65         FAULT signal from USB Power Protection Device STMPS2141         Active low           PC9         66         ENABLE signal to USB Power Protection Device STMPS2141         Active low           PC10<                                                                                                                                                                                                                    |              |      | _                                                 |                           |

| PB11         48         Drive TXEN signal to the DP83848J Ethernet MAC           PB12         51         Drive TXD0 signal to the DP83848J Ethernet MAC           PB13         52         Drive TXD1 signal to the DP83848J Ethernet MAC           PB14         53         USER I/O         Unprotected           PB15         54         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC           PC2         17         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC4         33         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC8         65         FAULT signal from USB Power Protection Device STMPS2141         Active low           PC9         66         ENABLE signal to USB Power Protection Device STMPS2141         Active low           PC10         78         USART4 TX         Unprotected           PC13                                                                                                                                                                                                                    |              |      |                                                   | Unprotected               |

| PB12         51         Drive TXD0 signal to the DP83848J Ethernet MAC           PB13         52         Drive TXD1 signal to the DP83848J Ethernet MAC           PB14         53         USER I/O         Unprotected           PB15         54         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC           PC2         17         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC4         33         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC8         65         FAULT signal from USB Power Protection Device STMPS2141         Active low           PC9         66         ENABLE signal to USB Power Protection Device STMPS2141         Active low           PC10         78         USART4 TX         Unprotected           PC11         79         USART4 RX         Unprotected           PC13                                                                                                                                                                                                                                     |              |      |                                                   |                           |

| PB13         52         Drive TXD1 signal to the DP83848J Ethernet MAC           PB14         53         USER I/O         Unprotected           PB15         54         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC         Unprotected           PC2         17         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC4         33         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC8         65         FAULT signal from USB Power Protection Device STMPS2141         Active low           PC9         66         ENABLE signal to USB Power Protection Device STMPS2141         Active low           PC10         78         USART4 TX         Unprotected           PC11         79         USART4 RX         Unprotected           PC13         7         USER I/O         Unprotected                                                                                                                                                                                                                                                   |              |      | •                                                 |                           |

| PB14         53         USER I/O         Unprotected           PB15         54         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC           PC2         17         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC4         33         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC8         65         FAULT signal from USB Power Protection Device STMPS2141         Active low           PC9         66         ENABLE signal to USB Power Protection Device STMPS2141         Active low           PC10         78         USART4 TX         VSART4 RX           PC12         80         USER I/O         Unprotected           PC13         7         USER I/O         Unprotected                                                                                                                                                                                                                                                                                                                                                           |              |      |                                                   |                           |

| PB15         54         USER I/O         Unprotected           PC0         15         Analog input from potentiometer. Used for test AD         Analog 0 to 3.3V           PC1         16         Drive MDC signal to the DP83848J Ethernet MAC           PC2         17         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC4         33         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC8         65         FAULT signal from USB Power Protection Device STMPS2141         Active low           PC9         66         ENABLE signal to USB Power Protection Device STMPS2141         Active low           PC10         78         USART4 TX         VOINTO STAND ST |              |      |                                                   | Unprotected               |

| PC0 15 Analog input from potentiometer. Used for test AD Analog 0 to 3.3V  PC1 16 Drive MDC signal to the DP83848J Ethernet MAC  PC2 17 USER I/O Unprotected  PC3 18 USER I/O Unprotected  PC4 33 USER I/O Unprotected  PC5 34 USER I/O Unprotected  PC6 63 USER I/O Unprotected  PC7 64 USER I/O Unprotected  PC8 65 FAULT signal from USB Power Protection Device STMPS2141 Active low  PC9 66 ENABLE signal to USB Power Protection Device STMPS2141 Active low  PC10 78 USART4 TX  PC11 79 USART4 RX  PC12 80 USER I/O Unprotected  PC13 7 USER I/O Unprotected  PC10 Unprotected  PC10 Unprotected  PC10 Unprotected  PC10 Unprotected  PC10 Unprotected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |      |                                                   |                           |

| PC1         16         Drive MDC signal to the DP83848J Ethernet MAC           PC2         17         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC4         33         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC8         65         FAULT signal from USB Power Protection Device STMPS2141         Active low           PC9         66         ENABLE signal to USB Power Protection Device STMPS2141         Active low           PC10         78         USART4 TX         Unprotected           PC11         79         USART4 RX         Unprotected           PC12         80         USER I/O         Unprotected           PC13         7         USER I/O         Unprotected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |      |                                                   | 1 .                       |

| PC2         17         USER I/O         Unprotected           PC3         18         USER I/O         Unprotected           PC4         33         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC8         65         FAULT signal from USB Power Protection Device STMPS2141         Active low           PC9         66         ENABLE signal to USB Power Protection Device STMPS2141         Active low           PC10         78         USART4 TX         VISART4 RX           PC12         80         USER I/O         Unprotected           PC13         7         USER I/O         Unprotected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |      | <u> </u>                                          | 7 110109 0 10 0.0 0       |

| PC3         18         USER I/O         Unprotected           PC4         33         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC8         65         FAULT signal from USB Power Protection Device STMPS2141         Active low           PC9         66         ENABLE signal to USB Power Protection Device STMPS2141         Active low           PC10         78         USART4 TX         VINDER I/O           PC12         80         USER I/O         Unprotected           PC13         7         USER I/O         Unprotected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |      |                                                   | Unprotected               |

| PC4         33         USER I/O         Unprotected           PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC8         65         FAULT signal from USB Power Protection Device STMPS2141         Active low           PC9         66         ENABLE signal to USB Power Protection Device STMPS2141         Active low           PC10         78         USART4 TX         VISART4 RX           PC11         79         USART4 RX         Unprotected           PC12         80         USER I/O         Unprotected           PC13         7         USER I/O         Unprotected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |      |                                                   |                           |

| PC5         34         USER I/O         Unprotected           PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC8         65         FAULT signal from USB Power Protection Device STMPS2141         Active low           PC9         66         ENABLE signal to USB Power Protection Device STMPS2141         Active low           PC10         78         USART4 TX         VSART4 TX           PC11         79         USART4 RX         Unprotected           PC12         80         USER I/O         Unprotected           PC13         7         USER I/O         Unprotected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |      |                                                   |                           |

| PC6         63         USER I/O         Unprotected           PC7         64         USER I/O         Unprotected           PC8         65         FAULT signal from USB Power Protection Device STMPS2141         Active low           PC9         66         ENABLE signal to USB Power Protection Device STMPS2141         Active low           PC10         78         USART4 TX         VSART4 TX           PC11         79         USART4 RX         Unprotected           PC12         80         USER I/O         Unprotected           PC13         7         USER I/O         Unprotected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |      |                                                   |                           |

| PC7 64 USER I/O Unprotected PC8 65 FAULT signal from USB Power Protection Device STMPS2141 Active low PC9 66 ENABLE signal to USB Power Protection Device STMPS2141 Active low PC10 78 USART4 TX PC11 79 USART4 RX PC12 80 USER I/O Unprotected PC13 7 USER I/O Unprotected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |      |                                                   | <u> </u>                  |

| PC865FAULT signal from USB Power Protection Device STMPS2141Active lowPC966ENABLE signal to USB Power Protection Device STMPS2141Active lowPC1078USART4 TXPC1179USART4 RXPC1280USER I/OUnprotectedPC137USER I/OUnprotected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |      |                                                   | <u> </u>                  |

| PC9         66         ENABLE signal to USB Power Protection Device STMPS2141         Active low           PC10         78         USART4 TX         VSART4 TX           PC11         79         USART4 RX         USER I/O         Unprotected           PC12         80         USER I/O         Unprotected           PC13         7         USER I/O         Unprotected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |      |                                                   |                           |

| PC10         78         USART4 TX           PC11         79         USART4 RX           PC12         80         USER I/O         Unprotected           PC13         7         USER I/O         Unprotected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |      | G .                                               |                           |